有一些电子设备需要频率高度稳定的交流信号,而LC振荡器稳定性较差,频率容易漂移(即产生的交流信号频率容易变化)。

在振荡器中采用一个特殊的元件——石英晶体,可以产生高度稳定的信号,这种采用石英晶体的振荡器称为晶体振荡器。

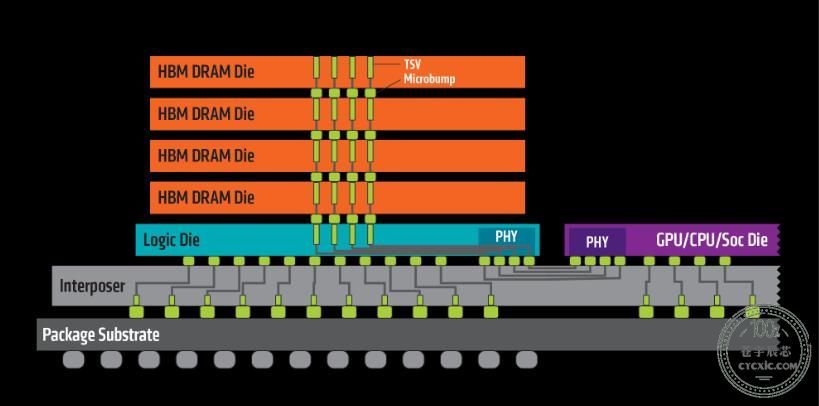

电子元器件的小型化趋势,有力促进了当下社会的发展进步,电子元器件越小,为主板节约的空间越大,因此,有人异想天开,如果能将晶振电路封装到IC芯片(如时钟芯片)内部将是多么wan美,就如同有源晶振在无源晶振的基础内置振动芯片,就无需外部的电容电阻等元器件了。

但实际出于各种原因,晶振并没有内置到IC芯片中。这究竟是为什么呢?

原因1、早些年,芯片的生产制作工艺也许还不能够将晶振做进芯片内部,但是现在可以了。这个问题主要还是实用性和成本决定的。

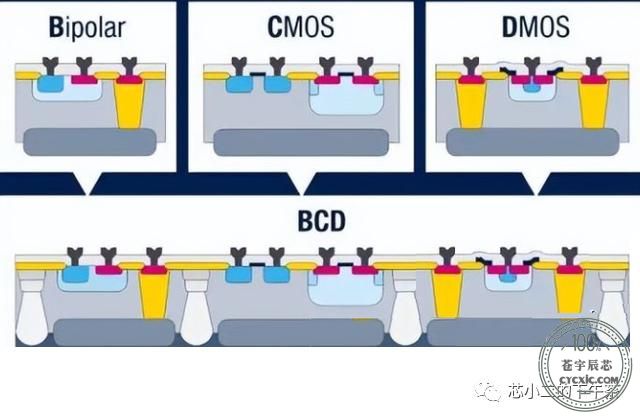

原因2、芯片和晶振的材料是不同的,芯片 (集成电路) 的材料是硅,而晶体则是石英 (二氧化硅),没法做在一起,但是可以封装在一起,目前已经可以实现了,但是成本就比较高了。

原因3、晶振一旦封装进芯片内部,频率也固定死了,想再更换频率的话,基本也是不可能的了,而放在外面, 就可以自由的更换晶振来给芯片提供不同的频率。

有人说,芯片内部有 PLL,管它晶振频率是多少,用 PLL 倍频/分频不就可以了,那么这有回到成本的问题上来了,100M 的晶振集成到芯片里, 但我用不了那么高的频率,我只想用 10M 的频率,那我为何要去买你集成了 100M 晶振的芯片呢,又贵又浪费。

我们通常所说的 "片内时钟", 是不是实际上片内根本没有晶振, 是有RC 振荡电路。

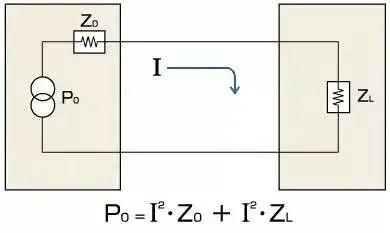

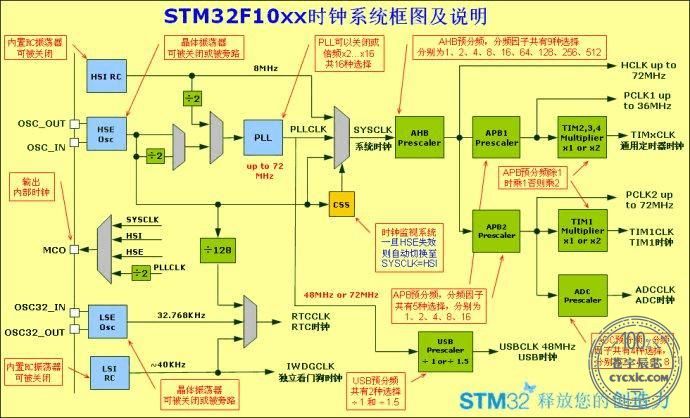

由图可以看出系统时钟的供给可以有3种方式,HSI,HSE,PLL。如果选用内部时钟作为系统时钟,其倍频达不到72Mhz,最多也就8Mhz/2*16 = 64Mhz。

如果使用内部RC振荡器而不使用外部晶振,请按照如下方法处理:

1)对于100脚或144脚的产品,OSC_IN应接地,OSC_OUT应悬空。

2)对于少于100脚的产品,有2种接法:

i)OSC_IN和OSC_OUT分别通过10K电阻接地。此方法可提高EMC性能。

ii)分别重映射OSC_IN和OSC_OUT至PD0和PD1,再配置PD0和PD1为推挽输出并输出'0'。此方法可以减小功耗并(相对上面i)节省2个外部电阻。

STM32时钟系统结构图

时钟是STM32单片机的脉搏,是单片机的驱动源。使用任何一个外设都必须打开相应的时钟。这样的好处就是,如果不使用一个外设的时候,就把它的时钟关掉,从而可以降低系统的功耗,达到节能,实现低功耗的效果。

STM32单片机的时钟可以由以下3个时钟源提供:

1、HSI:高速内部时钟信号STM32单片机内带的时钟 (8M频率), 精度较差。

2、HSE:高速外部时钟信号,精度高。来源:HSE外部晶体/陶瓷谐振器(晶振)HSE用户外部时钟

3、LSE:低速外部晶体32.768kHz主要提供一个精确的时钟源 一般作为RTC时钟使用。

文章整理自网络,如有侵权,请联系删除