SiC器件走向沟槽栅设计已经没有争议。但是目前大家比较头疼的,除了挖槽工艺之外,还有沟槽栅设计IP的问题。

关注的一个公众号搞了很多天马行空的沟槽栅设计。

直觉上:

1,设计IP这种东西,在我们的环境里不是事儿;

2,就算是个事儿,设计上一定有方法推陈出新。

最近发现一个似乎看起来比英飞凌半包沟槽和罗姆双沟槽都更好的技术路线。或者说,损耗比半包沟槽低,而可靠性比双沟槽好。同等工艺节点下。

除了还没有很认真地去评估长期可靠性是否能超过英飞凌,可以肯定比罗姆的可靠性好,最疑惑的问题是,为什么没有看到明显相似的做法。

因为本人所在公司还没有启动这个项目,所以具体思路不适合像二堡同学那样公开。

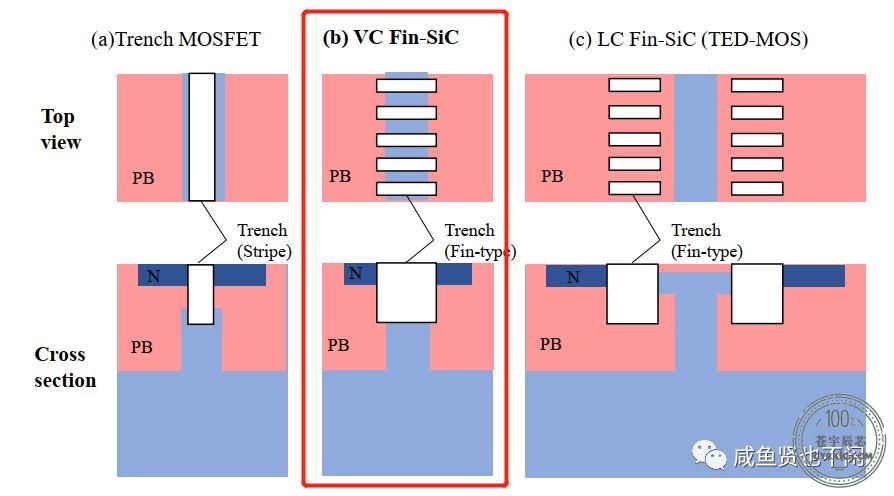

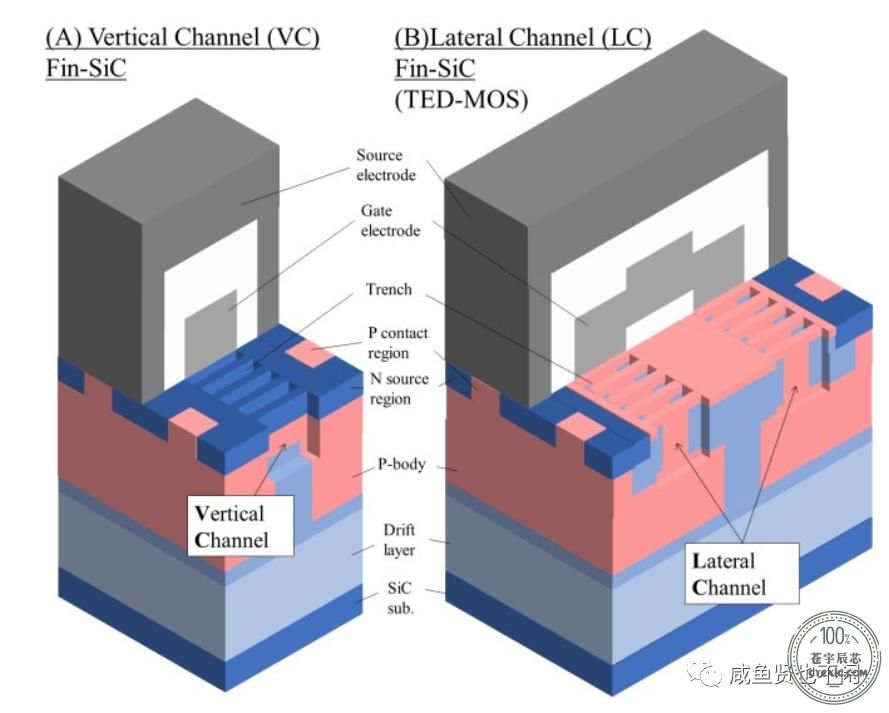

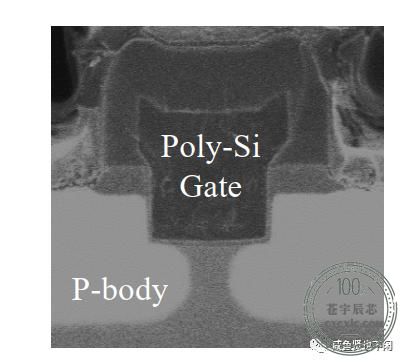

最近看到一个为了提升沟道宽度而采用Fin设计的SiC MOSFET方案。(ISPSD2023)

同等工艺尺寸,与单侧包角相比似乎不会有明显优势。

一方面,沟道长,并且jfet区域窄。

另一方面,Fin设计带来的沟道宽度增量,需要扣除损失的(11-20)晶向最强沟道的宽度。

电容的减小也不一定。

但是总体而言似乎值得尝试。

因为SiC的各向异性,有效的沟道宽度与版图上几何维度的宽度并不能划等号。

最好是增加沟道宽度的同时,最大程度地保留(11-20)晶向的沟道。其他方向事倍功半,需要更多的宽度才能弥补损失。

动态损耗还是需要降低弥勒电容。包角也不是唯一方式或者最佳方式。