功率MOSFET的输出电容是非常重要的一个参数,读过功率MOSFET数据表的工程师应该注意到:输出电容Coss会随着外加电压VDS的变化而变化,表现出非线性的特性,那么为什么会有这样的特性?

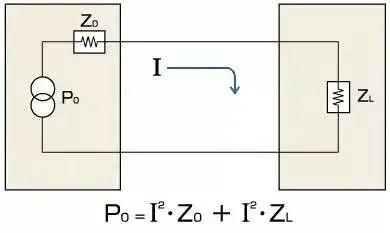

众所周知,当电容二端的电压增加时,就会形成对电容的充电电流,电容二个电极上的电荷量也会增加,因此,电容二端电压的变化是通过二个电极上的电荷的变化来实现。电容值的大小,和电容二个电极的面积A成正比,和二个电极的距离d成反比,和介质介电常数e成正比:

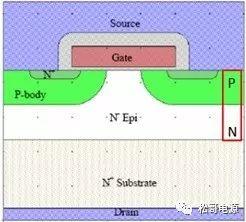

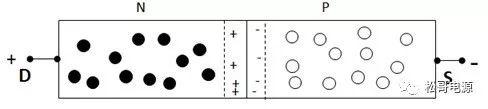

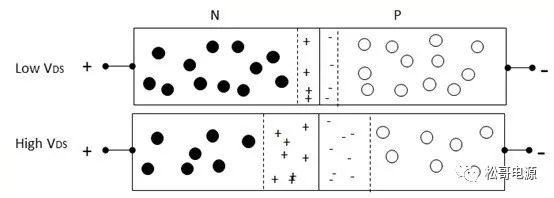

功率MOSFET的输出电容Coss实际上是漏极D和源极S的PN结的电容,漏极D和源极S加上电压VDS,PN结的耗尽层加宽,耗尽层、也就是空间电荷区内部的电荷数量增加,形成对PN结的充电电流,因此,这个特性表现出电容的特性,耗尽层在P区、N区内部的边界,就相当于电容的二个电极。

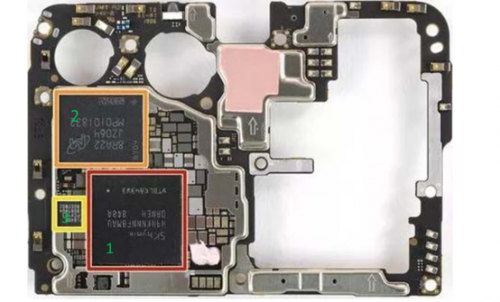

图1:功率MOSFET结构

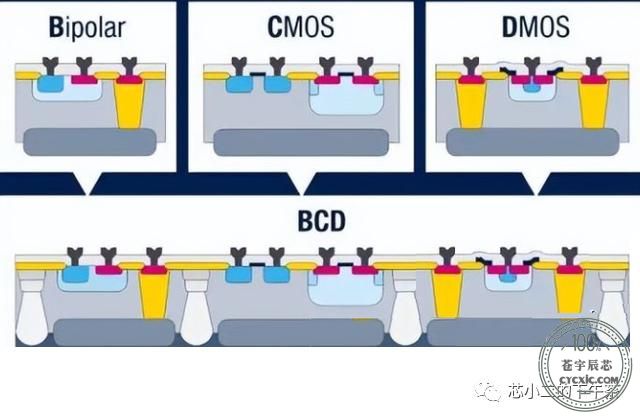

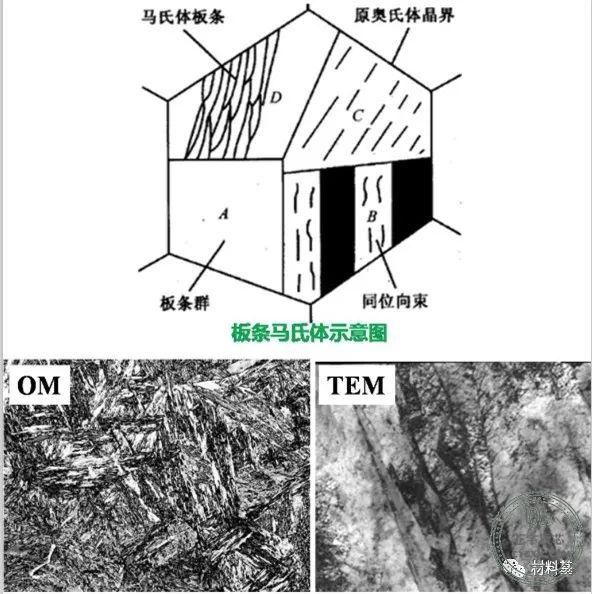

图2:功率MOSFET内部PN结耗尽层

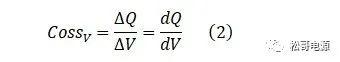

功率MOSFET外加电压VDS,输出电容Coss的电荷数量的改变,是通过耗尽层厚度的改变来实现。外加电压VDS增加,耗尽层厚度也相应的增加。在一定的外加偏置电压下,如果偏置电压发生非常小的变化,耗尽层厚度基本可以认为保持不变,耗尽层电荷的变化量与电压的变化量成正比,那么,在此外加偏置电压下,输出电容Coss为:

外加电压VDS比较小时,耗尽层的厚度也比较小,P区、N区初始的掺杂浓度相对比较高,自由导电的电子和空穴浓度比较高,因此,即使外加电压VDS发生很小的变化dV,空间电荷区也会产生非常大的电荷变化dQ,由公式2可以得到,偏置电压VDS比较小时,输出电容Coss电容值非常大。

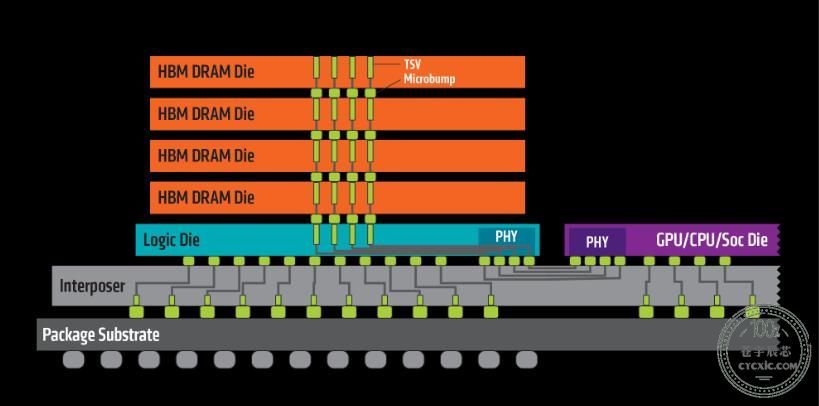

图3:不同VDS电压的PN结耗尽层

外加电压VDS增加到一定值,耗尽层厚度也增加到一定值,P区、N区的自由导电的电子和空穴浓度被大量消耗,浓度非常低,相对于低偏置电压VDS,为了得到同样的空间电荷区电荷变化值dQ,就需要更大的外加电压VDS的变化值dV1。由公式2可以得到,同样的dQ,dV1>dV,因此,当偏置电压VDS大时,Coss电容值就会变小。

同时,偏置电压VDS大时,耗尽层的厚度增大,相当于Coss电容的二个电极的距离增加,因此,会导致Coss电容值进一步的降低。

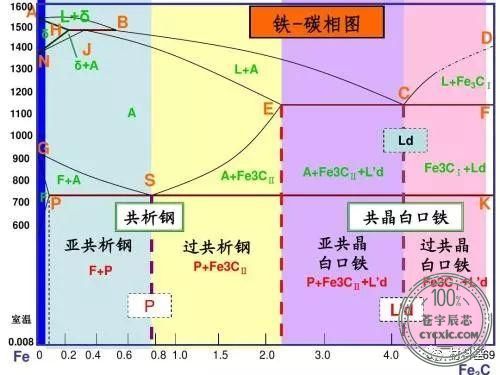

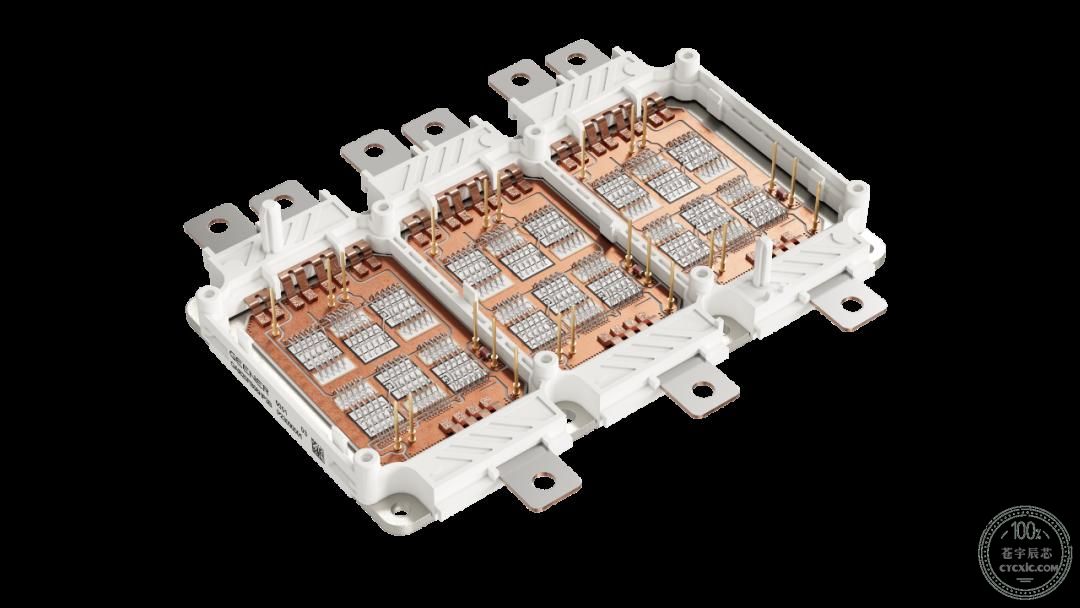

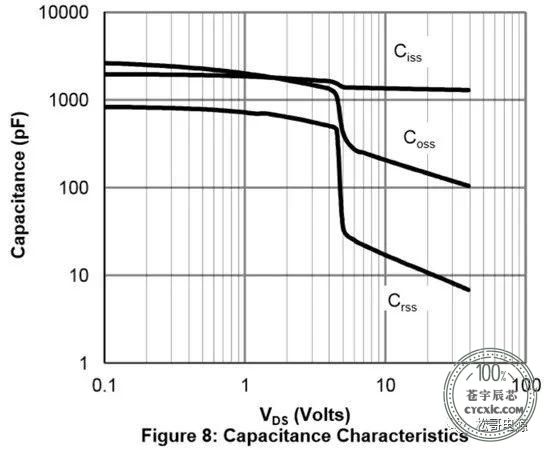

图4:AOT10N60的电容特性

综上所述:功率MOSFET的输出电容Coss会随着外加电压VDS的增加而降低,从而表现出非线性的特性;同样,Crss电容具有相同的特性。