1条回答

-

如果单元非常一致,散热非常好均匀、热平衡好,第一种情况发生,早期的平面工艺有时候就会看到这种损坏模式。现在新的工艺导致单元的密度越来越集中,产生的损坏通常用就是第二种。

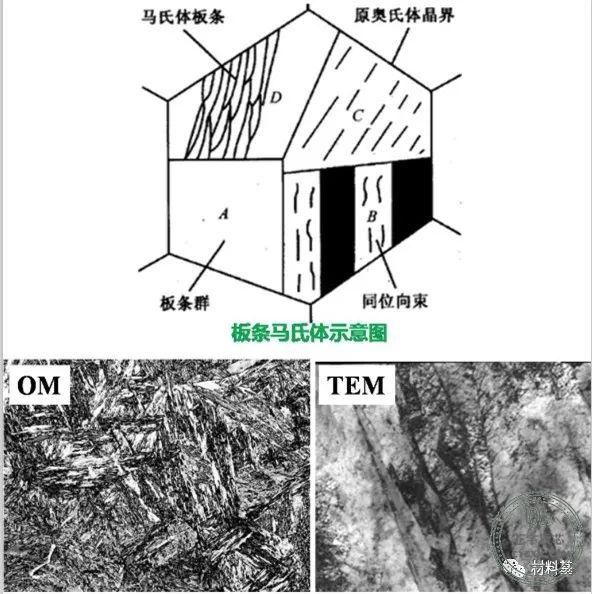

体内寄生三极管导通产生雪崩损坏,同时伴随着体内寄生三极管发生二次击穿,此时集电极电压在瞬态时间几个n秒内,减少到耐压的1/2,原因在于内部耗尽层载流子发生雪崩注入,电场电流密度很大,接近硅片临界电场。电流大,电压高,电场大,电离强,大量的空穴电流流过基区P体电阻RB,寄生三极管导通,集电极电压快速返回到基极开路时的击穿电压。增益大时,三极管中产生雪崩击穿,此耐压值低。

三极管中产生雪崩注入条件:电场应力,正向偏置热不稳定性。

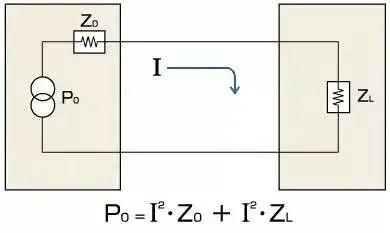

MOSFET关断时沟道漏极电流减小,感性负载使VDS升高,以维持ID电流的恒定,ID电流由沟道电流和位移电流组成。位移电流是体二极管耗尽层电流,和dV/dT成比例。VDS升高和基极放电、漏极耗尽层充电速度相关。漏极耗尽层充电速度和电容Coss、ID相关。ID越大,VDS升高越快。漏极电压升高,体二极管雪崩产生载流子,全部ID电流雪崩流过二极管,沟道电流为0。

很多的工程师问这样的一个问题:如果说UIS的雪崩损坏时电压通常会达到耐压值的1.2~1.3倍,可以明显看到电压有箝位,通俗说法就是波形砍头,那么对于100V的器件工作在105V或者110V是否安全?如上所述,100V的器件加上110V的电压不会损坏,那么安全的原则是什么呢?

对于设计工程师来说,所要求的就是在最极端的条件下设计的参数有一定的裕量,也就是从设计的角度来说保持系统的安全和可靠性,永远都排在最优先的位置。因此笔者建议的原则是:在动态的极端条件下瞬态的电压峰值不要超过MOSFET的额定值。0 举报

二極體建議的焊盤圖案為何?

半导体器件原理 2928人阅读

二極體使用上要注意的地方為何?

半导体器件原理 2881人阅读

關於稽納二極體,超過容許損失、發生故障時,端子間會短路嗎?會斷路嗎?

失效分析 2211人阅读

當ZD的Iz值低(10µA以下)時,會發生Vz值的振盪現象,原因為何?

半导体器件原理 1990人阅读

請問有沒有電晶體/二極體的物質安全資料表「MSDS(SDS)」?

半导体器件原理 1920人阅读

在端子彎曲加工上是否有應注意之要點?

半导体器件原理 1886人阅读

請告訴我二極體的型號說明。

半导体器件原理 1870人阅读

請問有沒有電晶體/二極體的物質安全資料表「MSDS(SDS)」?

半导体器件原理 1818人阅读

請告訴我電晶體的銲接條件為何?

半导体器件原理 1804人阅读

在晶體管的熱阻抗,熱量大,考量必須有條件的記載以上的基板面積時,此時的計算方法該如何做較好呢?

半导体器件原理 1779人阅读

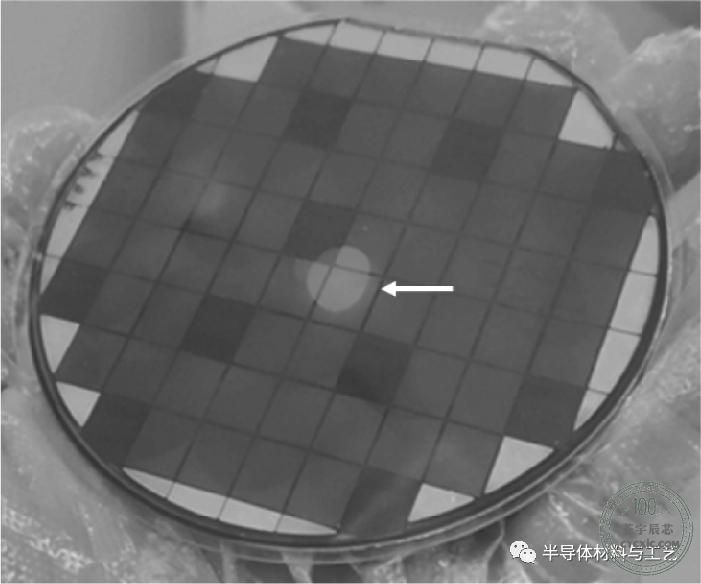

NMOS其中一个管子发现有损伤,但是右面放大的 L-PVC发现规律的3个灰度,这个和 烧伤有关联吗?

失效分析 1701人阅读

請告訴我電晶體的型號說明。

半导体器件原理 1698人阅读

電晶體建議的焊盤圖案為何?

半导体器件原理 1640人阅读

请教一个问题,元器件加速稳态寿命试验125度,1000小时等效于使用寿命多久,怎么计算?

失效分析 1614人阅读

何謂反向回復時間(trr)?

半导体器件原理 1535人阅读

工作溫度範圍

半导体器件原理 1508人阅读

何謂TVS二極體(ESD保護)?

半导体器件原理 1506人阅读

二極體的銲接條件為何?

半导体器件原理 1502人阅读

有關EDZS / EDZV的差異

半导体器件原理 1492人阅读

请问芯片的真空包装保存期限根据什么得到的?如何计算芯片存储的保存期限?

可靠性分析 1487人阅读

請告訴我二極體的型號說明。

问答

1 位搬砖人回复

二極體建議的焊盤圖案為何?

问答

1 位搬砖人回复

二極體的銲接條件為何?

问答

1 位搬砖人回复

二極體使用上要注意的地方為何?

问答

1 位搬砖人回复

何謂TVS二極體(ESD保護)?

问答

1 位搬砖人回复

何謂反向回復時間(trr)?

问答

1 位搬砖人回复

有關EDZS / EDZV的差異

问答

1 位搬砖人回复

有關UDZS / UDZV的差異

问答

1 位搬砖人回复

當ZD的Iz值低(10µA以下)時,會發生Vz值的振盪現象,原因為何?

问答

1 位搬砖人回复

請問有沒有電晶體/二極體的物質安全資料表「MSDS(SDS)」?

问答

1 位搬砖人回复

是否符合規範及ROHS指令?

问答

1 位搬砖人回复

二極體也可以使用手工焊接嗎?

问答

1 位搬砖人回复

是否可以將二極體進行迴焊?

问答

1 位搬砖人回复

在端子彎曲加工上是否有應注意之要點?

问答

1 位搬砖人回复

熱電阻:Rth是什麼?

问答

1 位搬砖人回复